Significant enhancements to the 16.6-2015 Constraint Manager release have been made in the following areas:

- Tag-based ECSet Mapping

- Single-Step Method for Creating Class-Class Relationships

- PCSets and SCSets Difference Reports

Read on for more details ...

Tag-based ECSet Mapping

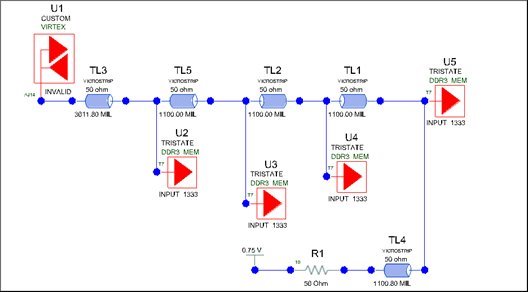

The process of applying an ECSet to target nets involves mapping the pins in the ECSet to the component pins in design for those nets. This process looks at many factors including signal_model assignments, pinuse, and RefDes to make a match. Difficulties can arise when the mapping is forced to rely solely on RefDes information and there is no one-to-one correlation between the RefDes information in the ECSet and the design. Take, for example, the following topology:

The mapping process has no way to distinguish between U2, U3, U4, and U5 except by RefDes. To address these issues, ECSet nodes now support tags (pin parameter) which can be used to uniquely identify a pin and remove any ambiguity. This can be used to lock the mapping between the ECSet and associated nets and will not be impacted by placement or RefDes changes.Tags can be defined in a design prior to ECSet extraction or ECSet application and can also be defined in SigXplorer.

Tags driven from SigXplorer

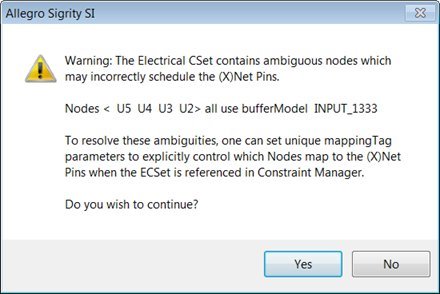

When the Update Constraint Manager command is executed, the following dialog is displayed:

Tags can be added in SigXplorer to the specified nodes using the Parameters pane:

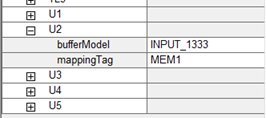

When the ECSet is applied to target nets, an interactive dialog is displayed where you assign the tags in the ECSet to the appropriate pins in the design:

This dialog shows the original log file at the bottom with new messages for cases where the ECSet has mapping tags but the design does not. The top portion contains pulldowns in the (X)Net section to use the Pin column or the Tag column to map the appropriate tags to the proper pins, and then update all the applicable objects which reference the same ECSet.

Tags Driven from Design

Tags can be added to pins in a design prior to extracting a topology into SigXplorer. The tags can be used to schedule a topology and when the topology is applied back to the design.

ECSet mapping tags are also supported in the front-to-back flow between Design Entry HDL and Allegro PCB Editor.

For more information see the Mapping ECSets to Nets Using Tags in Allegro Constraint Manager User Guide.

Single-Step Method for Creating Class-Class Relationships

This release includes a usability enhancement to ease the process of creating and updating class-class relationships between Net Classes and Region Classes in the Spacing domain.

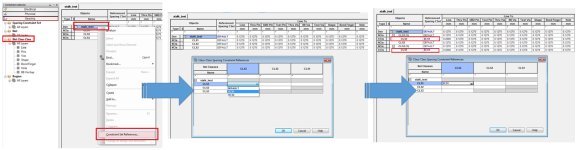

When you select the Constraint Set References command for a design, or a Region, a dialog displays a matrix of Net Classes. By clicking a cell, you can create Class-Class relationship between two Net/Region Classes and also apply an SCSet available from the drop-down list:

This solution works only if spacing CSets, Net Classes, and Region Classes are already in the design.

For more information, see Objects - Constraint Set References in Allegro Constraint Manager Reference Guide.

PCSets and SCSets Difference Reports

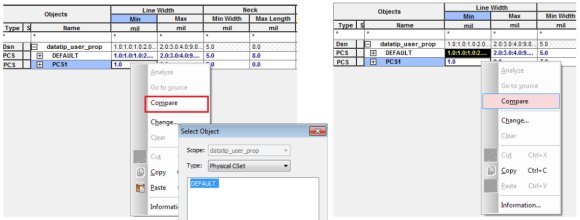

In this release, Constraint Manager is enhanced to provide support for comparing physical or spacing constraint sets. When a constraint set is selected, a new option Compare appears in the pop-up menu. On selecting a single constraint set, a Select Object dialog is displayed where you can select a constraint set to compare:

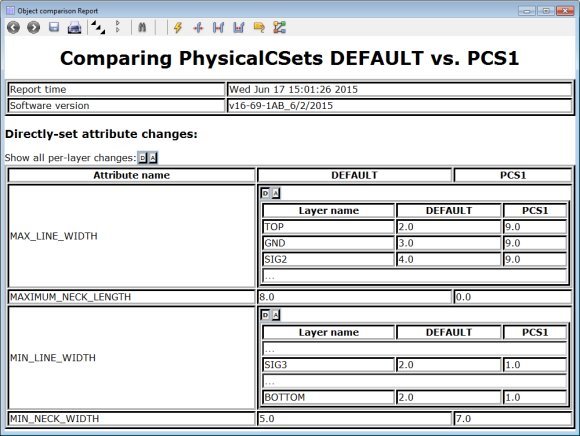

On comparing two CSets, an XML-based report is generated that opens in the built-in browser:

I welcome your feedback!

Jerry “GenPart” Grzenia