Normal

0

false

false

false

EN-US

X-NONE

X-NONE

Exposing metal through solder mask openings is as necessary

as it can be frustrating. For regular arrays and grids of pins of a flip chip,

embedding the openings directly in the padstack definition for the bumps is

perfect. But, what about for wire bond designs?

Fingers and power/ground rings need to be exposed so they

can be bonded to, but visibility of surrounding metal should be minimized. At

the same time, it is important that the openings themselves not have sharp

corners which could cause manufacturing concerns like the mask getting peeled

back.

As a result, it is not appropriate to use the solder mask

pads in the finger pad definitions (which wouldn't help with the rings,

regardless!). Instead, a smooth mask outline around sets of fingers in close

proximity is the best approach.

How, then, do you go about making this happen? With the

Cadence APD and SiP Layout tools in 16.6, the answer is the bond finger solder

masking tool. Keep reading to learn more about what this handy tool allows you to

do.

Creating Clean Solder Mask Openings

Near the end of your initial design of a substrate for a

package with one or more wire bonded dies, it comes time to define the solder

mask openings. APD and SiP Layout provide you with a tool specifically to

accomplish this task. You can find it under the Manufacture -> Create Bond

Finger Solder Mask menu item.

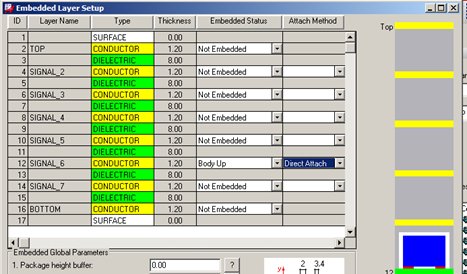

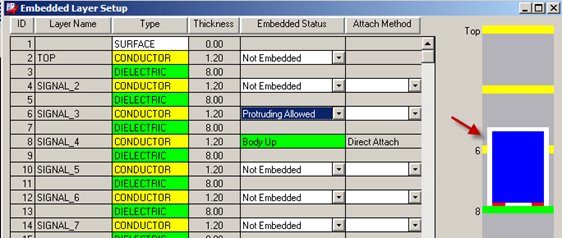

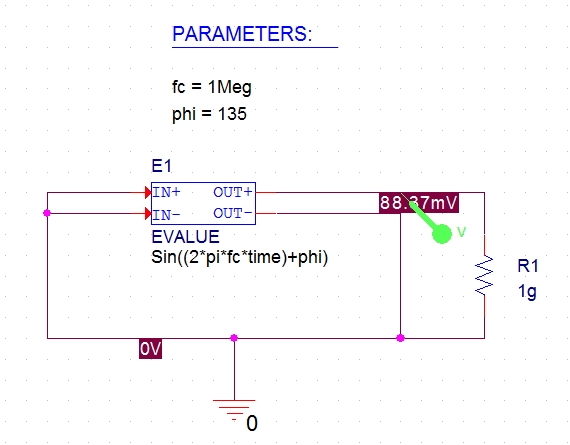

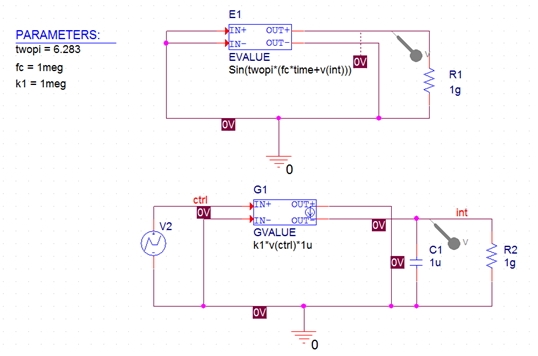

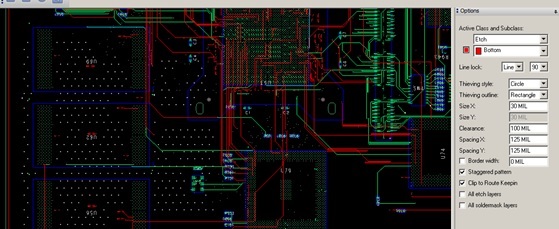

With a simple interface (see for yourself, below!), you get

all the controls that you need. There are two modes to give you the flexibility

you need, with different options for bond finger exposure and power/ground ring

openings.

![]()

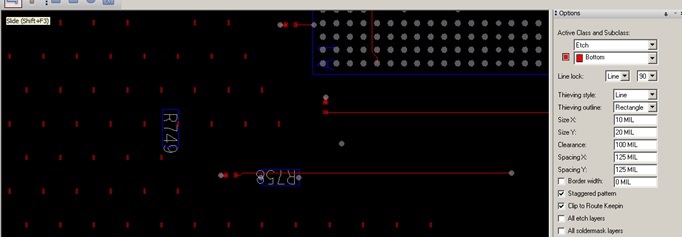

When creating mask openings for fingers, you should take

special note of the field at the very bottom. By controlling the intent width,

you can eliminate any potentially sharp corners on the inside of the mask shape

between fingers. This way, you get a smooth, clean opening around an entire

tier of fingers with one simple selection.

Conversely, for bonds to your rings, you can expose only the

pieces of the ring which have bonds to them. The mask openings can even be trimmed

to the edge of the shape to make sure no nearby clines are accidentally

exposed.

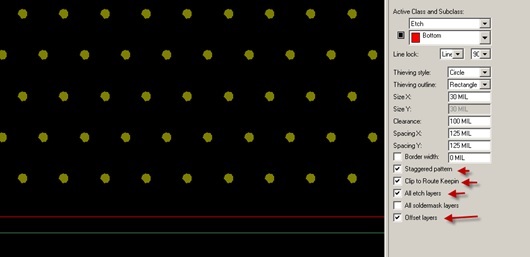

Do you have a need to create these types of masks around a

set of vias on your substrate layer? Do you have some pins, perhaps, where

using the padstack-embedded solder mask pad shape is not suitable? Fret not.

Turn on the "icp_soldermask_allow_pins" option in your User Preferences editor

and you can define masks for these objects with the same settings you have when

masking traditional fingers. How's that for flexibility?

What If I Need to Move My Bond Fingers After I've Generated My Shapes?

Fear not! ECO and design revisions are a fact of life. When

you receive an order that requires changes to the bond finger pattern, you can

make those changes knowing that, when complete, the mask openings can be

quickly and easily updated.

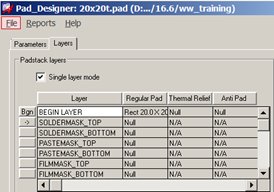

Using the same manufacturing command, make sure that you

have the "Delete existing solder mask" option enabled at the top of the options

(it is on in the screen shot above). This will automatically delete the old

shapes as you select the fingers you have moved or added, leaving just the new

mask. This ensures that you don't have overlapping masks that could result in

undesirable outlines or - even worse - the exposure of clines and vias that are

where one or more of the old fingers used to be.

What Tools Are Available for Validating My Solder Masks Are Correct?

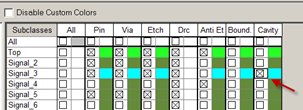

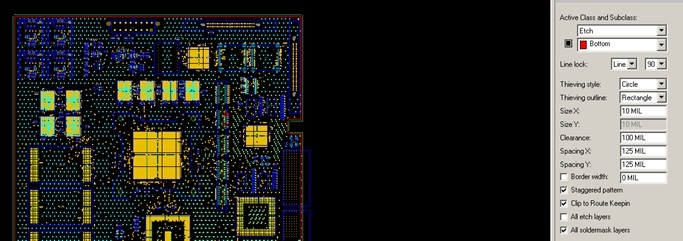

Once you have your solder masks defined (or after updating

them because of a design change request), it is important to validate that only

the right objects are going to be exposed during manufacturing of your

substrate.

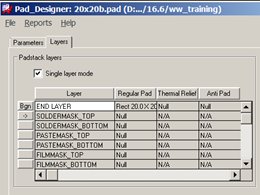

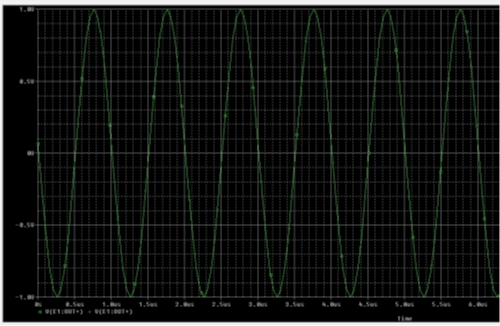

The APD and SiP Layout tools provide you with a number of

checks beyond the basic solder mask online DRCs. You can configure these under

the Assembly worksheet in Constraint Manager and run them from the Manufacture

-> Assembly Rules Checker... command, shown below with the 16.6 solder mask

rules:

![]()

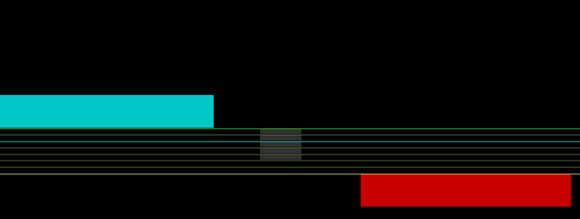

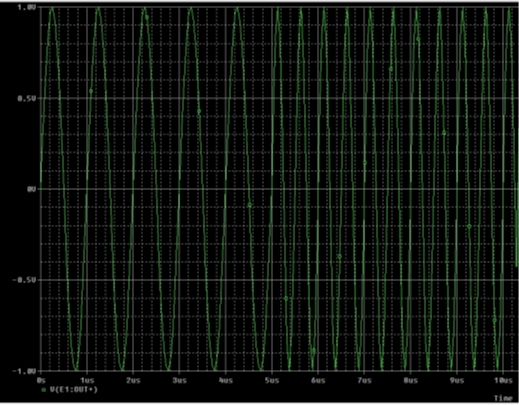

If you want to write your own

checks, you can use the RAVEL tool to define custom rules. Or, for pure

visualization of the metal exposed by the solder mask shapes (particularly

useful for documentation purposes), you can use the layer compare tool set,

which we covered in an earlier entry in this series. By doing a logical AND

between the solder mask layer and the corresponding substrate conductor layer,

you can create a layer showing only the metal that is visible through holes in

the solder mask. There's even the option of viewing things in the 3D Viewer,

where you can see the bond wires and their clearance from the masks as they get

close to the substrate! Talk about choices!

How Do You Define Your Solder Masks?

Armed with these tools, are you eager to make your design

flow more efficient? If you have an idea for how to make these tools even more

powerful, we would love to hear it. Give your Cadence support representative a

call and let us know your ideas. Just don't be surprised if, with the next

software release, you see your idea realized in the tool!

Jeff Gallagher

/* Style Definitions */

table.MsoNormalTable

{mso-style-name:"Table Normal";

mso-tstyle-rowband-size:0;

mso-tstyle-colband-size:0;

mso-style-noshow:yes;

mso-style-priority:99;

mso-style-qformat:yes;

mso-style-parent:"";

mso-padding-alt:0in 5.4pt 0in 5.4pt;

mso-para-margin-top:0in;

mso-para-margin-right:0in;

mso-para-margin-bottom:10.0pt;

mso-para-margin-left:0in;

line-height:115%;

mso-pagination:widow-orphan;

font-size:11.0pt;

font-family:"Calibri","sans-serif";

mso-ascii-font-family:Calibri;

mso-ascii-theme-font:minor-latin;

mso-fareast-font-family:"Times New Roman";

mso-fareast-theme-font:minor-fareast;

mso-hansi-font-family:Calibri;

mso-hansi-theme-font:minor-latin;

mso-bidi-font-family:"Times New Roman";

mso-bidi-theme-font:minor-bidi;}

![]()

![]()