![BoardSurfers: Cadence Allegro Blog]() Dynamic shapes; whether used on a negative or positive artwork layer, for power, ground, or signal; are the next most common element of a design after components and routing. The importance of using them effectively, then, can be the difference between a design that is DRC-free, ready on time, and easy to update for ECOs (Engineering Change Orders) and one that you seem to struggle with on a daily basis trying to force it to work.

Dynamic shapes; whether used on a negative or positive artwork layer, for power, ground, or signal; are the next most common element of a design after components and routing. The importance of using them effectively, then, can be the difference between a design that is DRC-free, ready on time, and easy to update for ECOs (Engineering Change Orders) and one that you seem to struggle with on a daily basis trying to force it to work.

As you move components, add and slide routing, or add features to improve signal integrity and manufacturing, you will impact the shapes in your design. An added via will require an extra void, but does that via also need thermal relief lines to the nearby shape? Will routing a trace too close to another result in a long sliver too narrow for the ground shape to squeeze between them for shielding? Does that return path via get too close to the edge of the shape, no longer able to connect over the pad center? Whatever you are doing, the action is likely to impact a shape on some layer of the design.

The Basics: Shape Types

The Cadence® Allegro® tool suite offers two types of shapes.

Static shapes, which are not managed by the system based on user design edits and dynamic shapes, which will automatically update voids as you go. These shapes can be very valuable in ECO flows where you do not want the system to make any changes to the shape you don’t see or sign off on.

Dynamic shapes, which update as design changes are made, allow you to easily see the impact of your edits and immediately undo and try another strategy if the impact on the shape is unacceptable. Dynamic shapes can be disabled - meaning no voiding is done (useful for a short term if you are making a large number of changes), rough/fast - meaning voiding is done but artwork checks and smoothing is not (much higher performance with localized updates based on design changes at the expense of having to do an update to final artwork later), and smooth, where all artwork prep is done in real-time as the design changes are made (great for smaller designs or later in the design, once you need 100% accurate shape outlines for SI analysis and other operations).

While many aspects of the two shape types are the same – the constraints they follow, for instance – the nature of dynamic shapes gives them advantages over static shapes. If they break into multiple etch pieces, islands and antenna areas can be automatically suppressed. Thermal connections can be updated in real-time. They can even have their fill style and parameters individually modified with instance-level customizations over the default global shape fill settings.

Voiding – How is it Done?

You’ve just routed a signal net through your ground shape. What impact does this have on the shape? First, required spacing will be determined. The basic holes for the cline, vias, and pins can then be cut from the shape. If your cline crosses multiple constraint regions, the spacing may be different in each of these. With vias and pins, multiple constraints may play a role – drill hole to shape clearance, regular or anti-pad clearance, even route keepout clearances for backdrilled pads. If you have set oversize clearances at the object, shape, or global shape parameters level, these are added for the basic hole generation.

Once the basic holes are generated, they are merged together to form compound void outlines. If you’ve routed a single net through the shape, the clines and vias are all connected together: you will see only one resulting hole. The hole and surrounding metal shape must then be analyzed for manufacturability. Acute angles will be trimmed. Narrow areas of the shape will be removed. And portions of the shape with no connections (known as islands) may be suppressed entirely.

Finally, the impact of these new voids is validated against surrounding elements. If the void around your cline causes a nearby ground via to disconnect from the shape, it may now need to be voided and thermally connected, instead. If your shape uses a cross-hatched fill, partial voids in the pattern may need to be filled to eliminate acid traps. Once the shape’s outline is deemed constraint-abiding and artwork ready, it is ready for you to see on the screen.

![Shape with islands deleted]()

Constraints – How do They Impact Voiding

Constraints are the lifeblood of your design. They allow the system to run checks and alert you to problems with connectivity, potential manufacturing issues, delay mismatches in critical nets, and many others. In a system with dynamic shapes, always meant to adjust themselves to remain a DRC-free state, what constraints drive this behavior and how?

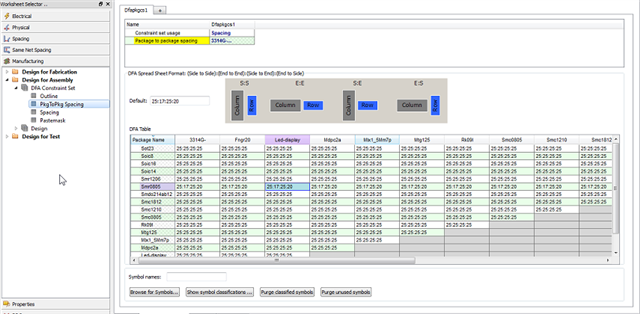

Physical spacing constraints from the spacing and same-net spacing categories, drive the clearance between the shape and nearby objects. These will include via, pin, drill hole, mechanical hole, cline, text, and shape to shape spacing. But, with the hierarchical, advanced constraint structure available with Allegro® Constraint Manager, this is taken to a new level. The spacing will differ depending on the nets of the conflict item and where it is on the board relative to constraint regions.

The base spacing constraints are augmented by the shape parameters. Available at the shape instance level or the global design level, these allow you to add any additional spacing needed between the shape and that object type. All locations in the database must always snap to the defined manufacturing units and accuracy. Depending on the accuracy of your design relative to object sizes, this oversize allows you to control how the tool compensates when it cannot meet the spacing rules exactly. You can also control the pad types used (do you need to void to the regular pad for vias, or maybe you need to void to the anti-pad) and the thermal connections needed. If a full contact is required for a pin, then the pin’s origin point must overlap with the shape.

![Shape rules in Constraint Manager]()

Lastly, in rare cases, you may need additional clearance on a specific object. Maybe you have a set of critical traces you want extra spacing around. Or this via shouldn’t be voided at all. Properties on those individual clines allow you to accomplish this exact tweak while maintaining it as you continue your design work.

Effectively Managing Your Dynamic Shapes and Voiding

With the number of rules to satisfy, it is reasonable to fear that having the system monitoring and managing this constantly while you work could lead to slow, inefficient design. Not so! Proper use of the tool will keep you moving fast without sacrificing design intent or feedback needed to make intelligent choices.

Place your components before you add your dynamic shapes. There is no need for the shapes to be there before there is anything to void to. Once you have your components laid out and are happy with the net scheduling, add your shapes. This should be done initially in rough or fast mode. While you are planning and placing initial routing, it is important to see if your shape integrity will be affected. But, it is far from the time when you need the shapes to be ready for artwork. After all, you can’t generate artwork when your components aren’t even connected! With initial routing complete, transition to smooth mode for your shapes. This will allow you to see the exact, detailed impact of your changes to the overall layout and metal density. If you have concerns about the metal coverage in areas of your design, Allegro offers tools to help monitor and guide you in this area, as well.

Avoid running the tool in smooth mode when you are making large changes to the entire design unless you are sure it is necessary. The time the tool spends trying to keep your shapes up to date during a batch update is likely to be far longer than just forcing them to update after all the complete batch of changes has been made.

Benefits of Updating to the Latest Release

With every release, whether it is major, minor, or quarterly update, improvements are made to fix bugs, add new functionality and improve the performance of both static and dynamic shapes. As a core technology in the PCB and IC package layout, these are always high on the list of focus areas.

In the recent 17.2 quarterly update, improvements to voiding accuracy around clines should be immediately noticeable. As your cline moves through constraint regions, not only does the trace neck up and down, but so does the shape to trace clearance. Clearance around the trace remains consistent across the entire path, as well, for SI reasons. If you need to add instance-level parameter overrides (or clear them) on multiple shapes, do so with the shape edit application mode. This will let you select them all together and make the changes, rather than applying changes one shape at a time.

![3D Canvas]()

Expect a similar level of new capabilities and enhancements, targeted to get your design to market as easy and as rapidly as possible, in the future.

![]()

![]()

Teardrops (also called fillets) are the blending area of a cline entry into a pad, while tapers are the gradual transition from one line-width to another along a path. These two core concepts appear in nearly any PCB or IC package substrate today. They act to smoothen the intersection of the two objects, eliminating acute angle acid traps while also contributing to better signal integrity along the path.

Teardrops (also called fillets) are the blending area of a cline entry into a pad, while tapers are the gradual transition from one line-width to another along a path. These two core concepts appear in nearly any PCB or IC package substrate today. They act to smoothen the intersection of the two objects, eliminating acute angle acid traps while also contributing to better signal integrity along the path.

Dynamic shapes; whether used on a negative or positive artwork layer, for power, ground, or signal; are the next most common element of a design after components and routing. The importance of using them effectively, then, can be the difference between a design that is DRC-free, ready on time, and easy to update for ECOs (Engineering Change Orders) and one that you seem to struggle with on a daily basis trying to force it to work.

Dynamic shapes; whether used on a negative or positive artwork layer, for power, ground, or signal; are the next most common element of a design after components and routing. The importance of using them effectively, then, can be the difference between a design that is DRC-free, ready on time, and easy to update for ECOs (Engineering Change Orders) and one that you seem to struggle with on a daily basis trying to force it to work.

Your design is near completion. Except that you’ve got an area of your plane shape that stubbornly refuses to fill, and you don’t know why. Understanding the rules involved and the tools available to help you figure out – and make changes, if needed, to get the result you want – is critical to make sure you aren’t wasting valuable design cycles.

Your design is near completion. Except that you’ve got an area of your plane shape that stubbornly refuses to fill, and you don’t know why. Understanding the rules involved and the tools available to help you figure out – and make changes, if needed, to get the result you want – is critical to make sure you aren’t wasting valuable design cycles.